Comment créer un émetteur UART série simple dans verilog HDL

La plupart des émetteurs récepteurs asynchrones universels (UART) que j'ai trouvés en ligne sont trop compliqués et difficiles à comprendre, ici je vais expliquer une théorie simple et aussi du code sur la façon d'en construire un.

Parlons d'abord du fonctionnement des émetteurs. Le principe de base est d'envoyer plusieurs bits de données sur une seule ligne. Dans notre émetteur, ces données sont parallèles, cependant pour réduire le nombre de fils nécessaires, nous utilisons une communication série qui est convertie en parallèle à la réception.

Les éléments de base dont nous avons besoin sont les suivants :

- Un diviseur d'horloge (notre compteur)

Cela nous permet d'envoyer des données à une certaine vitesse (débit en bauds). Notre récepteur échantillonnera et prendra les données bit par bit.

- Un registre à décalage

Nous devons savoir combien de bits nous transmettons à la fois, notre registre à décalage aura un bit de début, des bits de données, un bit de parité (facultatif), un bit de fin.

- Un diagramme d'état

Avant d'écrire du code, nous devons penser à ce que nous devons créer et le meilleur moyen est de créer un diagramme d'état de notre conception. Nous savons que pour un émetteur, nous avons besoin de 2 états, IDLE et TRANSMITTING.

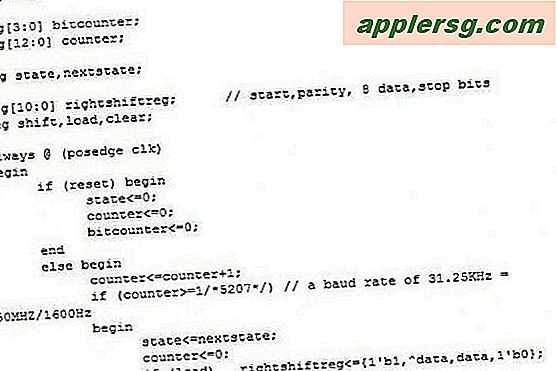

Après avoir eu un diagramme d'état, nous pouvons maintenant calculer ce que sera notre compteur. Cela se fait en utilisant :

compteur = vitesse d'horloge FPGA/débit en bauds

Dans cet exemple, j'utilise un débit en bauds de 9600, ce qui fait que mon compteur = 5208.

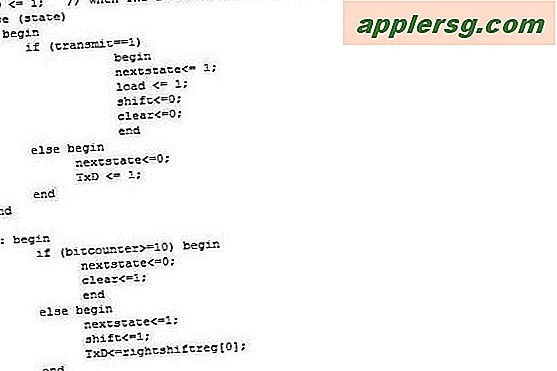

Enfin, nous calculons notre registre à décalage et finissons d'écrire notre machine d'état. Dans mon exemple de code, j'utilise un bit de début, un bit de parité, 8 bits de données et un bit de fin. Cela fait 11 bits au total.

Les deux images des étapes 2 et 3 réunies dans le même module complètent notre code d'émetteur requis pour programmer le FPGA. Ce code fonctionnera avec un autre FPGA connecté en série ou avec un hyperterminal Windows parmi d'autres matériels. Peut être facilement modifiable pour travailler avec beaucoup plus.

Enfin, nous créons un appareil de test pour corriger les erreurs et simuler notre programme avant de programmer le FPGA.

Ceci conclut l'émetteur. Veuillez laisser des commentaires si vous avez des questions ou si vous pensez qu'il manque quelque chose ici.

Conseils

L'émetteur et le récepteur doivent connaître le débit en bauds auquel les données sont envoyées.